Vhdl Program For Parity Generator Image

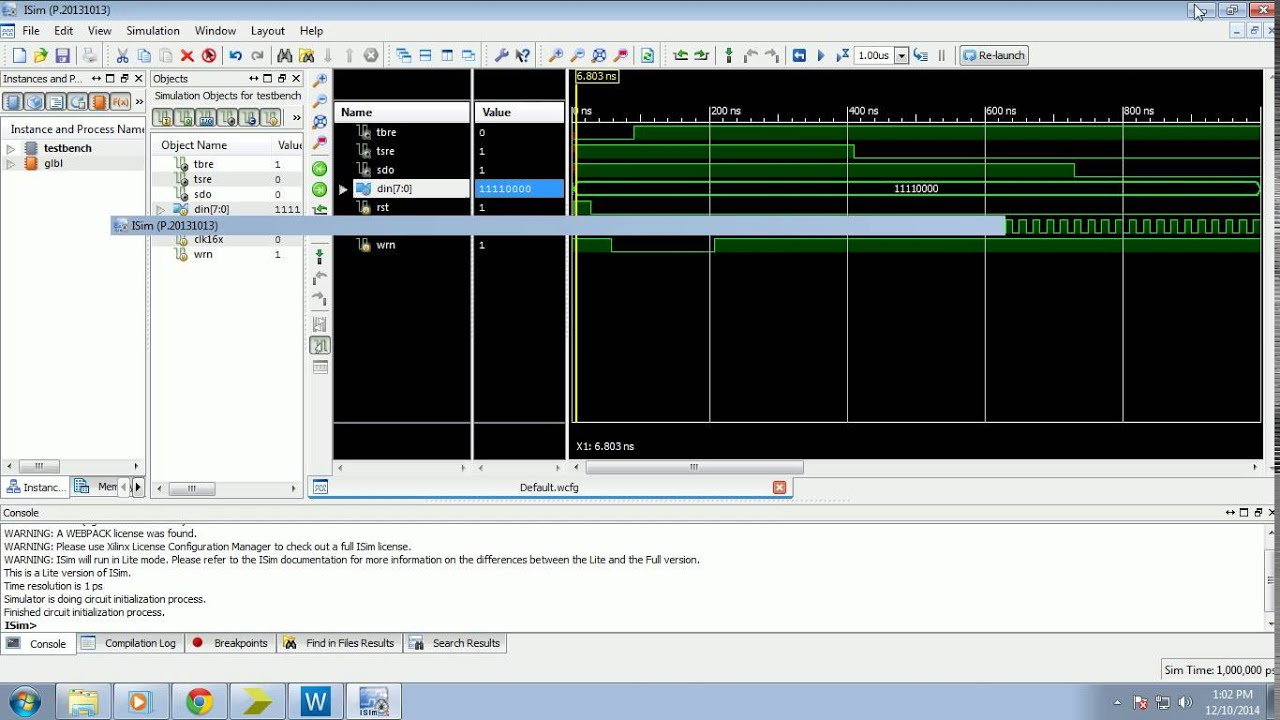

PROGRAM: - Library ieee; use ieee. Installing Windows On A Mac there. std_logic_1164.all; use vamsi.all; entity pg is port(d0,d1,d2,d3,d4,d5,d6,d7,d8:in bit;od:out bit); end pg; architecture str of pg is component xor2 port(a,b:in bit;y:out bit); end component; component not1 port(a:in bit;y:out bit); end component; signal e0,e1,e2,e3,f0,f1,a0,ev:bit; begin x1:xor2 port map(d0,d1,e0); x2:xor2 port map(d2,d3,e1); x3:xor2 port map(d4,d5,e2); x4:xor2 port map(d6,d7,e3); x5:xor2 port map(f0,f1,a0); x6:xor2 port map(a0,d8,ev); x7:not1 port map(ev,od); end str; SIMULATION OUTPUT.

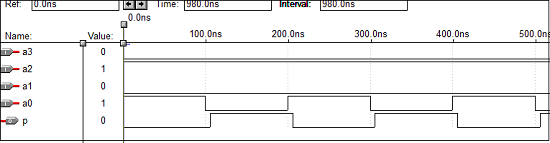

I'm trying to do a simple project in VHDL. The specification is that it takes 4 bit data as input, and generates a parity bit (I will use this small module in UART later.) My approach is that, if I sum each bit of the data, I get the number of 1's inside of it. Then, if it's even I generate 0, else 1. I wrote such code for this purpose: library IEEE; use IEEE.std_logic_1164.all; use IEEE.numeric_std.all; use IEEE.std_logic_unsigned.all; entity parity_checker is Port ( data: in STD_LOGIC_VECTOR (3 downto 0); even_parity_bit: out STD_LOGIC); end parity_checker; architecture Behavioral of parity_checker is signal sum_of_1s: std_logic_vector (2 downto 0):= '000'; begin sum_of_1s. You could just XOR data elements together and use that as data parity in the same way you're evaluating sum_of_1s(0). Foundation Of Solid Mechanics Fung Pdf Reader.